## **Components and Systems Based on Printed Metal Oxide Electronics and Silicon Devices**

Zur Erlangung des akademischen Grades eines

#### **DOKTOR-INGENIEURS**

von der KIT-Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT)

genehmigte

#### DISSERTATION

von

#### **M.Sc. Alexander Scholz**

geb. in Schwetzingen

Tag der mündlichen Prüfung: Hauptreferentin: Korreferent: 19. November 2021Prof. Dr. rer. nat. Jasmin Aghassi-HagmannProf. Dr. Mehdi Baradaran Tahoori

# Kurzfassung

Gedruckte Elektronik ermöglicht die Anfertigung elektrischer Bauteile und Systeme auf großflächigen, flexiblen Trägersubstraten. Des Weiteren wird durch berührungsfreie Druckverfahren, wie dem Tintenstrahldruck, eine flexible, dezentrale Fertigung elektronischer Bauteile und Systeme ermöglicht. Dies erlaubt unter anderem das Split-Manufacturing sicherheitskritischer elektronischer Komponenten, sowie eine größtmögliche Designfreiheit im Sinne von freien Formfaktoren und nicht standardisierter Strukturen mit unterschiedlichsten Abmessungen im Bereich von wenigen Mikrometern bis hin zu mehreren Millimetern.

Durch die genannten technologischen Aspekte bildet die gedruckte Elektronik einen interessanten Gegenpol zur klassischen hochintegrierbaren, miniaturisierten Silizium-Elektronik. Durch eine komplementäre Nutzung der Vorteile beider Technologien entstehen neuartige Synergien und Applikationen in Form von hybriden Systemen. Während hybride Lösungen, basierend auf passiven gedruckten Bauteilen und elektrisch leitfähigen Komponenten bereits kommerziell erhältlich sind, bleiben komplexe Systeme, die sowohl passive, als auch aktive, gedruckte elektronische Bauteile nutzen, noch selten. Um ganzheitliche, gedruckte sowie hybride elektronische Systeme zu ermöglichen, sind diverse Bausteine erforderlich. Hierzu zählen leichtgewichtige Möglichkeiten zur Datenspeicherung sowie Komponenten, die sich selbst mit Energie versorgende Systeme ermöglichen und insbesondere Schaltungen zur sicheren, eindeutigen Identifizierbarkeit ganzheitlicher, gedruckter Systeme für das Internet der Dinge.

Die hier vorliegende Arbeit befasst sich mit, durch Tintenstrahldruck hergestellten, elektronischen Bauteilen, Schaltkreisen, sowie hybriden Systemen. Es wurden Lösungen zu aktuellen wissenschaftlichen Fragestellungen in den Bereichen effizienter gedruckter Speicherbausteine, nachhaltiger elektronischer Systeme, sowie der hardwarebasierten Sicherheit, auf Basis gedruckter Elektronik, erforscht und entwickelt.

Zur Datenspeicherung für gedruckte Systeme wurde ein, mittels Tintenstrahldruck hergestellter, Memristor entwickelt. Das Bauteil wurde vollumfänglich im Hinblick auf die Speicherung digitaler Information, charakterisiert. Die erzielten Ergebnisse zeigen, dass der Memristor als nichtflüchtiges Speicherelement genutzt werden kann.

Um ganzheitliche, nachhaltige elektronische Systeme zu ermöglichen wurde ein gedruckter Vollweggleichrichter entwickelt. Durch die Verwendung von Electrolyte-Gated Transistoren mit einer Schwellspannung von nahe-null Volt, ist die Schaltung in der Lage kleine Wechselspannungen, wie sie von piezoelektrischen Energy Harvestern erzeugt werden, gleichzurichten. Der, mittels Tintenstrahldruck hergestellte, Vollweggleichrichter wurde elektrisch vollumfänglich charakterisiert.

Zur Erzeugung einzigartiger Identifikationsmerkmale wurden zwei Implementierungenmöglichkeiten physikalisch unklonbarer Funktionen entwickelt. Dieser Ansatz nutzt die unvorhersehbare, intrinsische Variation gedruckter Bauteile als hardwarebasiertes Sicherheitsfeature. Eine untersuchte Implementierung basiert auf einer Crossbar-Anordnung integrierbarer Electrolyte-Gated Transistoren. Die zweite Implementierungsvariante nutzt Inverterstrukturen, ebenfalls auf Basis von Electrolyte-Gated Transistoren, zur Erzeugung der einzigartigen Systemantworten. Beide Varianten wurden sowohl mit Hilfe von elektrischen Simulationen, als auch experimentell untersucht. Die Inverter-basierte, intrinsische Variationsquelle wurde des Weiteren vollständig in ein Silizium-basiertes Gesamtsystem integriert und hinsichtlich ihrer Sicherheitsmetriken untersucht. Das Gesamtsystem bildet ein hybrides System, bestehend aus gedruckten Bauteilen sowie klassischer Silizium-Elektronik, zur Erzeugung einzigartiger Systemantworten.

## Abstract

Printed electronics, due to its manufacturability using printing technology, allows for fabrication on large areas and the usage of flexible substrates and thus enables novel applications. Non-impact printing technology, such as inkjet-printing, permits for flexible, decentralized manufacturing of electronic devices and systems. This further facilitates split-manufacturing in security-critical electrical components, as well as a maximum in design flexibility in terms of free form factors and non-standardized structures with different geometrical sizes, reaching from a few micrometers up to several millimeters.

Based on the technological benefits printed electronics offers, it provides an interesting counterpart to classical silicon-based electronics, which is usually densely integrated on miniaturized, rigid areas. By utilizing both technologies in a complementary manner, novel systems in the form of hybrid systems can be enabled. Whilst hybrid systems, incorporating passive printed components and electrically conductive wiring concepts, are already commercialized, complex printed systems, which also utilize active components remain rare. To enable more complex (hybrid) systems, various building blocks are required. This includes possibilities for lightweight, printed data storage, the capability to provide sustainable, self-powered printed components and especially circuits for secure, unique identification for holistic printed systems, deployed in the internet of things.

The presented thesis focuses on inkjet-printed electronic devices, circuits and hybrid systems. It investigates solutions for current scientific questions in the area of efficient data storage, sustainable electronics and hardware-based security in printed electronics. For data storage, an inkjet-printed memristor is developed. The device is fully electrically evaluated with a focus on its data storage capabilities. Furthermore, the printed device is of special interest due to its easy manufacturability and integration capabilities. The experimental analysis reveals that the developed memristor is highly suitable as lightweight non-volatile memory device.

In order to enable sustainable electronic systems, an inkjet-printed full-wave rectifier based on near-zero threshold voltage electrolyte-gated transistors is developed and fully electrically characterized. The circuit is capable for small alternating voltage rectification of low-frequency vibration energy harvesters in the sub-volt region. This provides an important building block in enabling sustainable, selfpowered electronic systems. The inkjet-printed full-wave rectifier is evaluated by electrical simulation and experimentally.

To tackle hardware-based security for printed electronics, two implementations for inkjet-printed physically unclonable functions are developed and presented. For unique identification, intrinsic variation in active printed devices are exploited. One implementation is based on a crossbar architecture, incorporating integrable electrolyte-gated transistor cells. The second implementation, the so-called differential circuit physically unclonable function, is based on inverter structures, which provide the basis for unique response generation. Both physically unclonable functions are evaluated using an electrical simulation-based approach and experimentally. The differential circuit approach is furthermore fully integrated within a silicon-based electronic platform environment and serves as intrinsic variation source in a hybrid system. The hybrid system physically unclonable function is fully verified regarding performance metrics and is capable to generate highly unique responses for secure identification.

## Preface

First, I would like to thank Prof. Jasmin Aghassi-Hagmann, as my main supervisor, for providing me the opportunity in pursuing this thesis. This includes numerous scientific discussions, encouragement in presenting the obtained results, up to funding acquisition and in improving my overall scientific skill set. Also, thanks to Prof. Mehdi Tahoori for all scientific discussions and valuable feedback, which helped in improving my scientific skill set as well and for being the second examiner of this thesis. I would also like to thank Prof. Uli Lemmer and Prof. Axel Sikora for valuable scientific feedback.

Thanks go to all my colleagues from the MEARGEM graduate school, the HSO and the KIT. Special thanks go to Gabriel Marques, Xiaowei Feng, Surya Singaraju, Dennis Weller, Farhan Rasheed, Andres Rösch, Ahmet Erozan, Felix Neuper, Thorsten Grün, Mayukh Bhattacharyya and Daniel Gerig in being great scientific sparring partners and providing feedback and help over the past years. I especially thank my close colleague Lukas Zimmermann, who made the whole PhD time a great joy. I will always remember the good times we had in Washington D.C. and Chengdu, next to the numerous technical, scientific and personal discussions. I thank my former students Axel Rombach and Hongrong Hu, who both did a remarkable job. Further thanks go to Prof. Jürgen Giehl for introducing me to printed electronics during my undergraduate studies.

I would also like to express my gratitude towards everyone that made work at various premises at the HSO and KIT an unbureaucratic venue. Thanks go to Siri Weisse for her support regarding organizational topics during the whole PhD time. Special thanks go to Liane Koker, Zehua Chen and Ulrich Gengenbach from the KIT-IAI for the great cooperation.

I thank the Ministry of Science, Research and Arts of the state of Baden-Württemberg for the financial support through the Landesgraduiertenförderung.

Furthermore, I thank my family and friends for their invaluable support, on which I can always rely on.

Abschließend möchte ich mich ganz besonders bei meinen Eltern Birgitta und Alfredo, sowie meiner Schwester Isabelle, für all die Möglichkeiten die ihr mir eröffnet habt und für eure unermüdliche Unterstützung, bedanken.

# Contents

| Ku | rzfas               | sung .  |                                                            | i             |

|----|---------------------|---------|------------------------------------------------------------|---------------|

| Ab | strac               | ct      |                                                            | iii           |

| Pr | eface               | •       |                                                            | v             |

| Ab | brev                | iations |                                                            | xi            |

| 1  | <b>Intro</b><br>1.1 |         | <b>n</b>                                                   | <b>1</b><br>5 |

| 2  | Bac                 | kgroun  | d & State of the Art                                       | 7             |

|    | 2.1                 | Fabrica | tion Processes & Structuring of Thin-Film Devices          | 7             |

|    |                     | 2.1.1   | Conventional Printing Technologies for Printed Electronics | 7             |

|    |                     | 2.1.2   | Drop-on-Demand Piezo-Inkjet Printing for Printed           |               |

|    |                     |         | Electronics                                                | 9             |

|    |                     | 2.1.3   | Laser Ablation                                             | 10            |

|    | 2.2                 | Printed | Thin-Film Transistors & Circuits                           | 12            |

|    |                     | 2.2.1   | Printed Thin-Film Transistors                              | 12            |

|    |                     | 2.2.2   | Printed Circuits                                           | 14            |

| 3  | New                 | Conce   | epts in Printed Electronics                                | 17            |

|    | 3.1                 | Sustain | able Energy with Printed Rectifiers                        | 17            |

|    | 3.2                 | New Pa  | aradigms in Computing using Memristors                     | 19            |

|    | 3.3                 | Hardwa  | are-Based Security with Physically Unclonable Functions .  | 23            |

|    |                     | 3.3.1   | Printed Physically Unclonable Functions                    |               |

|    |                     | 3.3.2   | Evaluation of Physically Unclonable Functions              | 27            |

| 4 | Inkj | et-Printed Devices                                            | 31         |

|---|------|---------------------------------------------------------------|------------|

|   | 4.1  | Inkjet-Printed Electrolyte-Gated Transistors                  | 31         |

|   | 4.2  | Inkjet-Printed Memristor                                      | 35         |

|   | 4.3  | Conclusion                                                    | 42         |

| 5 | Inki | et-Printed Circuits                                           | 45         |

| - | 5.1  | Inkjet-Printed Low-Voltage Rectifier                          | 46         |

|   | 5.2  | Inkjet-Printed Low-Voltage Security Circuits                  | 52         |

|   |      | 5.2.1 Printed Crossbar PUF Architecture                       | 53         |

|   |      | 5.2.2 Simulation-Based Printed Crossbar PUF Metric Evaluation | 57         |

|   |      | 5.2.3 Proof of Concept Printed Crossbar PUF Evaluation        | 61         |

|   |      | 5.2.4 Printed Differential Circuit PUF Architecture           | 62         |

|   |      | 5.2.5 Simulation-Based DiffC-PUF Metric Evaluation            | 65         |

|   |      | 5.2.6 Proof of Concept DiffC-PUF Core Evaluation              | 72         |

|   | 5.3  | Conclusion                                                    | 73         |

| 6 | Hvb  | rid Systems                                                   | 77         |

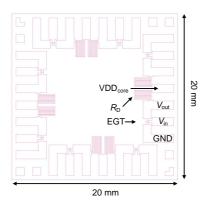

| Ŭ | 6.1  | Embedded Differential Circuit Physically Unclonable           | •••        |

|   |      | Function Platform                                             | 77         |

|   |      | 6.1.1 Platform with Silicon-Based PUF Core                    | 82         |

|   |      | 6.1.2 Platform with Printed Electronics-Based PUF Core        | 88         |

|   | 6.2  | Conclusion                                                    | 95         |

| 7 | Sum  | mary and Outlook                                              | 97         |

| ' | 7.1  |                                                               | <b>9</b> 7 |

|   | 7.2  | Outlook                                                       | 99         |

|   | 1.2  | Outlook                                                       | 77         |

| Α | Арр  | endix                                                         | 01         |

|   | A.1  | Materials                                                     | 101        |

|   |      | A.1.1 Electrolyte-Gated Transistors                           | 101        |

|   |      | A.1.2 Memristor                                               | 101        |

|   | A.2  | Fluid Preparation                                             | 102        |

|   |      | A.2.1 Electrolyte-Gated Transistors                           |            |

|   |      | A.2.2 Memristor                                               | 102        |

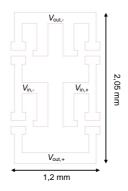

|   | A.3  | Layouts                                                       |            |

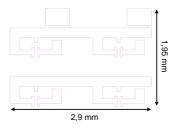

|   |      | A.3.1 PE-Based DiffC-PUF Core Layout                          | 103        |

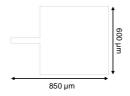

| <ul> <li>A.3.2 Inkjet-Printed Low-Voltage Full-Wave Rectifier Layout 104</li> <li>A.3.3 Inkjet-Printed Memristor Layout</li></ul> |

|-----------------------------------------------------------------------------------------------------------------------------------|

| List of Figures                                                                                                                   |

| List of Tables                                                                                                                    |

| List of Publications                                                                                                              |

| Bibliography                                                                                                                      |

# **Abbreviations**

| $\mathbf{AC}$  | Alternating Current                     |

|----------------|-----------------------------------------|

| ADC            | Analog-to-Digital Converter             |

| Ag             | Silver                                  |

| Au             | Gold                                    |

| BA             | Bit Aliasing                            |

| BE             | Bit Error                               |

| $\mathbf{BU}$  | Buffer Amplifier                        |

| $\mathbf{CC}$  | Compliance Current                      |

| CMOS           | Complementary Metal-Oxide-Semiconductor |

| $\mathbf{CNT}$ | Carbon Nanotube                         |

| CPU            | Central Processing Unit                 |

| $\mathbf{CR}$  | Chromium                                |

| CRP            | Challenge-Response Pair                 |

| CSPE           | Composite Solid Polymer Electrolyte     |

| DAC            | Digital-to-Analog Converter             |

| DC             | Direct Current                          |

| DEMUX          | Demultiplexer                           |

|                |                                         |

| DiffC Differential Circuit                                         |                                                                                                                                                                                       |  |  |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DoD                                                                | Drop-on-Demand                                                                                                                                                                        |  |  |

| DPI                                                                | Dots Per Inch                                                                                                                                                                         |  |  |

| ECM                                                                | Electrochemical Metallization Memory                                                                                                                                                  |  |  |

| EDL                                                                | Electrical Double Layer                                                                                                                                                               |  |  |

| EGFET                                                              | Electrolyte-Gated Field-Effect Transistor                                                                                                                                             |  |  |

| EGT                                                                | Electrolyte-Gated Transistor                                                                                                                                                          |  |  |

| EKV                                                                | Enz-Krummenacher-Vittoz                                                                                                                                                               |  |  |

| $\mathbf{FF}$                                                      | Form Factor                                                                                                                                                                           |  |  |

| FHD                                                                | Fractional Hamming Distance                                                                                                                                                           |  |  |

| FHE                                                                | Flexible Hybrid Electronics                                                                                                                                                           |  |  |

|                                                                    |                                                                                                                                                                                       |  |  |

| FIB                                                                | Focused Ion Beam                                                                                                                                                                      |  |  |

| $FIB \\ H_2InN_3O_1$                                               | 0                                                                                                                                                                                     |  |  |

|                                                                    |                                                                                                                                                                                       |  |  |

|                                                                    | 0                                                                                                                                                                                     |  |  |

| $H_2InN_3O_1$                                                      | <sup>0</sup> Indium (III) Nitrate Hydrate                                                                                                                                             |  |  |

| $H_2InN_3O_1$<br>HD                                                | <sup>0</sup> Indium (III) Nitrate Hydrate<br>Hamming Distance                                                                                                                         |  |  |

| H <sub>2</sub> InN <sub>3</sub> O <sub>1</sub><br>HD<br>HRS        | <sup>0</sup> Indium (III) Nitrate Hydrate<br>Hamming Distance<br>High-Resistance State                                                                                                |  |  |

| H <sub>2</sub> InN <sub>3</sub> O <sub>1</sub><br>HD<br>HRS<br>I/O | <sup>0</sup> Indium (III) Nitrate Hydrate<br>Hamming Distance<br>High-Resistance State<br>Input-/Output                                                                               |  |  |

| $H_2InN_3O_1$ $HD$ $HRS$ $I/O$ $I-V$                               | <ul> <li><sup>0</sup> Indium (III) Nitrate Hydrate</li> <li>Hamming Distance</li> <li>High-Resistance State</li> <li>Input-/Output</li> <li>Current-Voltage</li> </ul>                |  |  |

| $H_2InN_3O_1$ $HD$ $HRS$ $I/O$ $I - V$ $IC$                        | <ul> <li>Indium (III) Nitrate Hydrate</li> <li>Hamming Distance</li> <li>High-Resistance State</li> <li>Input-/Output</li> <li>Current-Voltage</li> <li>Integrated Circuit</li> </ul> |  |  |

- LAE Large-Area Electronics

- LP Low-Pass

- LRS Low-Resistance State

- MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

- MUX Multiplexer

- NL Noise Level

- **OE** Organic Electronics

- **OFET** Organic Field-Effect Transistor

- **OLED** Organic Light-Emitting Diode

- **OTFT** Organic Thin-Film Transistor

- PC Personal Computer

- PCB Printed Circuit Board

- PCE Power Conversion Efficiency

- PE Printed Electronics

#### $\mathbf{PEDOT}:\mathbf{PSS}$

Poly(3,4ethylenedioxythiophene):Poly(styrenesulfonate)

- PEN Polyethylene Naphthalate

- PET Polyethylene Terephthalate

- PUF Physically Unclonable Function

- PVA Polyvinyl Alcohol

- **RFID** Radio Frequency Identification

- **RH** Relative Humidity

| RMS                                                                             | Root Mean Square                               |

|---------------------------------------------------------------------------------|------------------------------------------------|

| $\mathbf{RS}$                                                                   | Resistive Switching                            |

| $\mathbf{Rt}\mathbf{R}$                                                         | Roll-to-Roll                                   |

| SCLC                                                                            | Space-Charge Limited Current                   |

| SCPI                                                                            | Standard Commands for Programmable Instruments |

| SEI                                                                             | Semiconductor Electrolyte Interface            |

| SEM                                                                             | Scanning Electron Microscopy                   |

| Si                                                                              | Silicon                                        |

| $\mathbf{TFT}$                                                                  | Thin-Film Transistor                           |

| TGEI                                                                            | Top-Gate Electrolyte Interface                 |

| VCM                                                                             | Valence Change Memory                          |

| VCR                                                                             | Voltage Conversion Ratio                       |

| $\mathbf{Zn}(\mathbf{NO_3})_2 \cdot \mathbf{6H_2O}$<br>Zinc Nitrate Hexahydrate |                                                |

| ZnO                                                                             | Zinc Oxide                                     |

| μC                                                                              | Microcontroller                                |

## 1 Introduction

The rapid development in densely integrated semiconductor devices forms the backbone of a modern, digitized society. Integrated circuits (ICs), based on monocrystalline silicon (Si), provide the basis for communication, data processing and digital information exchange in general. With state of the art central processing units (CPUs) exhibiting several billions of transistors on square millimeter sized areas. Production of ICs is done in globally distributed foundries. However, foundries supporting current technology nodes, are scarce. This is mainly reasoned by the intense cost in establishing a modern foundry, exhibiting several billions of dollars, in combination with the required infrastructure for energy, water, gas and waste management.

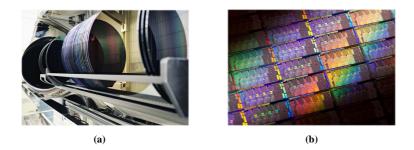

While IC integration densities on miniaturized areas are unmatched, combined with production in large quantities, initial costs in IC designs, customization and redesigns are expensive. This leads to centralized production, in combination with low customization possibilities due to the enormous cost barriers faced in production. Figure 1.1 shows examples for Si-based electronics, from wafer to IC, in the form of a microprocessor architecture.

In 1977, scientists report on electrical conductivity in polymers by doping of polyacetylene [1]. On the long term, this discovery enabled novel research and business areas based on organic electronics (OE). Reasons for the increased interest in OE is in reduction of processing complexity, compared to conventional manufacturing methods, as well the possibility for fabrication on large areas and flexible substrates at low processing temperatures. Furthermore, OE allows for so-called "green" electronics utilizing bio-compatible materials [2]. Popular examples for organic electronics are organic light-emitting diodes (OLEDs), which

Figure 1.1: Exemplary images for Si-based electronics from wafer to IC. (a) Multiple bare silicon wafers. Source: Infineon Technologies. (b) ICs in the form of an Intel "Sandy Bridge" microprocessor architecture, based on 32 nm technology node, on processed wafer. Source: Intel Free Press, reproduced under CC BY-SA 2.0 license, https://creativecommons.org/licenses/by-sa/2.0/.

are successfully commercialized in display technology mainly using evaporation techniques, currently still at high temperatures and rigid substrates [3, 4]. However, transparent, flexible large-area OLED displays are already successfully demonstrated [5].

To further enable large-area electronics (LAE) on flexible substrates for low-cost electronics, the idea of using printing technology to process organic and inorganic materials to build electronic devices from a liquid phase emerged [6–9]. With various printing technologies at disposal, different needs can be addressed. Roll-to-roll (RtR) printing solutions are capable for high-throughput fabrication over large areas, whilst non-impact printing technologies, such as inkjet-printing, offer decentralized manufacturing with highly dynamic design customization of the print product. This makes inkjet-printing an interesting and disruptive manufacturing technology in the era of the internet-of-things (IoT) and fourth industrial revolution.

Due to the immense application potential of PE and persistent shortcomings in realizing complex, fully printed systems, such as reduced performance in active devices and performance reliability in general, interest in flexible hybrid electronics (FHE) increased [14–17]. By merging both technologies benefits, classical

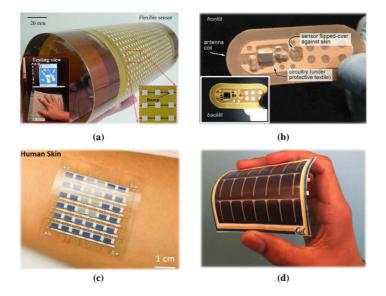

Figure 1.2: Examples for PE-based electronics and hybrid systems. (a) Screen-printed sensor array for large-area sensing on flexible substrates [10], © 2009 IEEE. (b) Flexible, adhesive RFID patch for sweat electrolyte detection. The patch also incorporates Si-based electronics for signal processing and communication [11], © 2014 IEEE. (c) Screen-printed active matrix electrochromic display on flexible substrate. Reprinted with permission from [12], © 2016 American Chemical Society. (d) Flexible solar cell combined with battery. The battery electrodes are printed [13]. Reproduced under CC BY 4.0 license, https://creativecommons.org/licenses/by/4.0/.

Si-based electronics, as well as PE, novel systems in the form of hybrid systems can be designed. With the already mentioned unmatched integration capabilities and device speed, Si-based electronics provides the backbone for high-speed, wireless communication and control, whilst PE enables for additive, large-area manufacturing on flexible substrates [15–20]. Possible application scenarios are in large-area sensing, healthcare, smart packaging and logistics. Examples for PE-based electronics and hybrid systems can be seen in Figure 1.2. In order to realize high-performance flexible hybrid systems, thinned Si-based ICs can be incorporated into the flexible substrate [21, 22].

Initially, the term LAE was used and enabled by hydrogenated amorphous silicon (*a*-Si:H)-based thin-film-transistor (TFT) technology [23–25], which allows fabrication on large areas. The need for LAE arise from emerging display technology, where TFTs were - and still are - used as control elements in active matrix configurations [26–28]. With increasing demand in higher performance TFTs for active matrix displays utilizing the aforementioned OLEDs, semiconducting metal oxides, such as zinc oxide and indium-gallium-zinc oxide, gained attention [29–32].

Conventional fabrication of LAE, utilizing TFTs on both, rigid [33,34] and flexible substrates [31,35–38] is possible using evaporation, sputtering and various deposition methods, such as plasma-enhanced chemical vapor deposition [39]. Due to reduced device performance of TFTs, hybrid systems are proposed [37,40,41]. A combination of Si-based electronics as signal conditioning backend and a LAE TFT-based frontend offers a hybrid approach, harvesting both technologies benefits in a complementary manner. Besides the large-area manufacturability, cost per transistor is massively increased in conventionally manufactured TFT technology, in comparison to the densely integrated transistors in ICs [28], due to the increased feature size of a TFT.

Solution processing and printing of inorganic semiconductors in the form of silicon [42, 43], as well as oxide semiconducting materials over a wide variety is possible [44–47]. However, TFT-based LAE with solution-processed, or printed devices, in combination with Si-based electronics, to enable holistic hybrid systems, remain scarce. Nonetheless, LAE in the form of printed structures (strain, force, temperature), without active devices, are broadly reported [48–51].

PE-based electronics, may it be organic, inorganic, (semi)-conducting materials, passive or active devices, fabricated on small or large areas, utilizing rigid and flexible substrates, offers a broad field of novel applications. This highlights the importance of a holistic development approach for promising PE-based devices, circuits and hybrid systems in order to shape and enable the future of electronics, which will increasingly impact our everyday life.

In this work, inkjet-printed electronic devices, circuits and hybrid systems are investigated.

### 1.1 Structure of the Thesis

In the following, the structure of the thesis, which incorporates inkjet-printed electronic devices, circuits and hybrid systems, is listed.

- Chapter 2 introduces fabrication and structuring methods for thin-film devices. This includes printing technologies for printed electronics with a focus on drop-on-demand piezo-inkjet printing. The general working principle of laser ablation, for solid material structuring, is discussed. In the following, an introduction to printed transistors is given. A focus is on inkjet-printed electrolyte-gated transistors (EGTs). The chapter concludes with the description of state of the art printed circuits.

- Chapter 3 presents new design and hardware concepts in printed electronics. This includes sustainable energy, new paradigms in computing and hardware-based security. For sustainable energy, a focus is on processing of low-voltage, low-frequency systems harvesting environmental energy. Furthermore, novel paradigms in computing are introduced with a focus on memristors, which have shown great potential as memory devices and as general building blocks in Beyond-von-Neumann computing and neural networks. Hardware-based security introduces the concepts of physically unclonable functions, which can be used for the creation of a device specific fingerprint.

- Chapter 4 shows the fabrication routine for inkjet-printed, top-gate bottomcontact EGTs on lasered substrates, which are used for all further investigated circuits and hybrid systems.

Furthermore, inkjet-printed memristors, which show great potential as (non-volatile) memory devices are investigated. The devices are fully electrically characterized and switching characteristics are reported. Furthermore, statistical analysis regarding cycle-to-cycle and device-to-device variability is presented and an investigation regarding the device's conduction mechanism is made.

• Chapter 5 presents the results for novel inkjet-printed circuits, based on EGTs. This incorporates an inkjet-printed full-wave rectifier for low alternating voltage rectification and a full electrical characterization of the circuit.

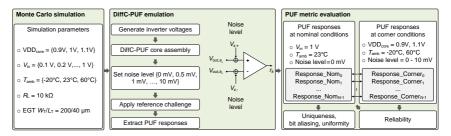

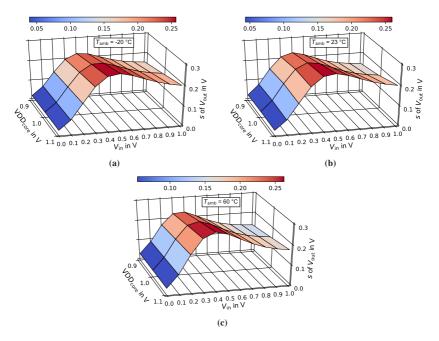

Furthermore, two inkjet-printed physically unclonable functions are designed and investigated, using electrical simulation. A focus is on the printed PUF core intrinsic and systematic variation. Moreover, emulated Si-based control logic systematic variation is incorporated for holistic PUF metric investigation of the proposed printed PUFs. For both PUF implementation, the printed PUF cores are fabricated and electrically evaluated.

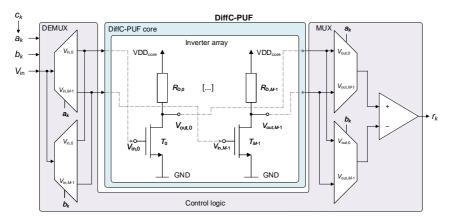

• Chapter 6 shows the obtained experimental results for the embedded differential circuit (DiffC)-PUF as hybrid system platform, incorporating a printed DiffC-PUF core and a Si-based control logic. For reference design in a first step, a Si-based DiffC-PUF core is fully evaluated for commissioning of the platform. It shows that the Si-based PUF core allows for extremely reliable, unique key generation, which can be utilized for integration of PUF schemes in software-communication layers.

Finally, a PE-based DiffC-PUF core is integrated within the system and fully investigated, with respect to voltage levels and PUF performance metrics. The PE-based PUF is capable to generate unique responses and is highly suitable for fingerprinting.

• Chapter 7 summarizes the results obtained in this thesis and highlights possible future investigation scenarios.

# 2 Background & State of the Art

In this chapter, methods for TFT fabrication and device structuring, as they are used for this work, are discussed. An overview of popular printing technologies for PE is given. The main focus regarding printing technologies is on drop-ondemand piezo-inkjet printing. Also, solid material structuring via laser ablation is introduced. Thin-film transistors based on printable organic and inorganic semiconducting materials are shown, with special focus on low-voltage electrolytegated transistors. A brief overview about state of the art, advanced printed circuits with emphasis on digital and analog circuit building blocks are given.

## 2.1 Fabrication Processes & Structuring of Thin-Film Devices

### 2.1.1 Conventional Printing Technologies for Printed Electronics

Printing techniques, requiring a printing form, are labeled as conventional printing processes. The printing form, which holds the desired design, is used to transfer the print material onto the carrier substrate [7,52]. Changes in the design require a change in the print form. Popular conventional printing technologies for PE are gravure-, flexo-, screen- as well as offset- printing [7,53]. The mentioned printing technologies offer roll-to-roll compatibility and allow for high throughput printing. Primary differences are in various processing parameters, including

Figure 2.1: Pilot printing line "Gallus RCS 330", using conventional printing methods for PE. Source: Innovationlab GmbH.

printing resolution, throughput, mechanical complexity as well as requirements regarding processable fluids, to name but a few.

Due to possible multi-modal requirements for PE-based applications, printing technologies can be used either standalone or as combined systems. Figure 2.1 shows partially a pilot printing line utilized for PE, based on conventional, RtR printing technology. Next to the printing elements, modules for substrate and fluid treatment, such as heating elements or systems for removal of electrostatic charge [54] need to be deployed.

In Table 2.1, several core performance parameters of above mentioned conventional printing methods for PE are compared.

| Printing<br>technology | Print resolution<br>(µm) | Print speed $(m \cdot min^{-1})$ | Fluid surface tension $(mN{\cdot}m^{-1})$ | Fluid viscosity<br>(Pa·s) |

|------------------------|--------------------------|----------------------------------|-------------------------------------------|---------------------------|

| Gravure                | 50 - 200                 | 8 - 100                          | 41 - 44                                   | 0.01 - 1.1                |

| Flexographic           | 30 - 80                  | 5 - 180                          | 13.9 - 23                                 | 0.01 - 0.5                |

| Screen                 | 30 - 100                 | 0.6 - 100                        | 38 - 47                                   | 0.5 - 5                   |

| Offset                 | 20 - 50                  | 0.6 - 15                         | /                                         | 2 - 5                     |

Table 2.1: Comparison between several conventional printing technologies for PE, adapted from [7].

The absence of a parameter is denoted by (/).

### 2.1.2 Drop-on-Demand Piezo-Inkjet Printing for Printed Electronics

Drop-on-demand (DoD) piezo-inkjet is a non-impact printing technology. To realize a print-design, no physical print form is required. Layouts can be fully adapted in software and transferred from a personal computer (PC) to the machine in form of a digital picture matrix.

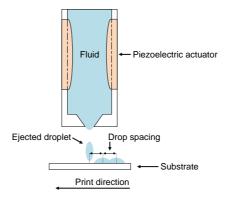

Figure 2.2: Schematic for a DoD piezo-inkjet printhead ejecting a droplet on a carrier substrate within a defined drop spacing.

In piezo-inkjet printing, the fluid is ejected from the printer nozzle, due to a volume change in the fluid reservoir of the printhead, onto the desired substrate area [52], as visualized in Figure 2.2. This is enabled through to a voltage-controlled, mechanical actuation of a piezoelectric transducer [55], within the printhead. Typical jetting frequencies are in the range of 1 kHz - 20 kHz [55, 56]. With droplet volumes in the picoliter range, in combination with precise, on-demand droplet ejection, DoD piezo-inkjet printing allows for fabrication at a minimum material usage and thus reduced material waste.

Requirements for inkjet-printable fluids are high. Viscosity, surface tension, density, size of polymers, molecular weight and particle size in general, to name

but a few, impact inkjet-printing behavior [57–60]. Inkjet-printability and droplet formation of fluids can be estimated with the dimensionless, inverse Ohnesorge number Z, as shown in Equation 2.1. With *Re* being the Reynolds and *We* the Weber number [55].

$$Z = \frac{Re}{\sqrt{We}} \tag{2.1}$$

Values for Z between 1 < Z < 10 show proper inkjet-printing behavior of fluids, according to Reis and Derby [56]. Jang et al. [60] report on Z values ranging from  $4 \le Z \le 14$ , for optimal inkjet-printing behavior of certain fluids, processed with piezo-inkjet printers.

Drop-on-demand piezo-inkjet printer offer various options for printhead parameter configuration, which allows to adapt for different fluids. This includes jetting frequency, dedicated pulse waveform settings, applied voltage level on the piezoelectric actuator, static pressure level and fluid reservoir temperature. Usually, a heatable vacuum plate for substrate placement is employed. This is required to control pinning of the fluid on substrate surface impact. Surface impact effects, based on ejected droplet speed, in combination with pinning of the fluid on the substrate, are further important points in DoD piezo-inkjet printing, when high resolution print results are required. The print resolution, for digital printing technologies, is given as dots per inch (DPI). Commercially available inkjet-printers, for research and development, such as the Fujifilm Dimatix DMP series provide print resolutions up to 5080 DPI. This allows for 5 µm-spaced droplet ejection, also referred to as drop spacing.

#### 2.1.3 Laser Ablation

Laser ablation enables non-contact structuring of solid materials. This is achieved by high optical irradiation intensities with a strongly focused laser beam on a solid material, which leads to material removal [61–63]. The ablation process is achieved above a threshold fluence, which is heavily influenced by a material's absorption characteristics, laser pulse duration and laser wavelength [61–63]. For high quality machining of solid materials with high thermal diffusivity, fast laser pulses (ps to fs) are required [64]. Simplified, when the laser pulse duration is longer then the material's heat diffusion time, the material is vaporized due to predominantly thermal interaction [65, 66], which can result in ejected blobs of melted material and surface shock, which also can lead to damage of material in the heated zone [66]. However, the fluence heavily influences the pre-dominantly laser-/material interaction [62, 63].

Figure 2.3: Conceptual, simplified schematic of a laser ablation process.

With laser pulses exceeding the material's thermal diffusivity, the material is directly exposed to high amounts of energy, which can lead to non-thermal, photochemical ablation mechanisms. The material is forced in a state of plasma due to the occurring direct ionization and expands in the form of a energetic dense, visible vapor plume [62, 66], as schematically visualized in Figure 2.3. This form of ablation is called cold ablation and allows for precise micro-machining of solid material. However, the dense vapor plume may contain liquid or solid material, which may lead to debris on the material surface [63]. Furthermore, due to the expansion of the vapor plume, surface shock effects can occur.

### 2.2 Printed Thin-Film Transistors & Circuits

### 2.2.1 Printed Thin-Film Transistors

Material and substrate possibilities are broad and allow for manifold options in printed TFT realization. Organic TFTs (OTFTs), also labeled organic field-effect transistors (OFETs), mainly incorporate semiconducting materials, based on conjugated polymers and conjugated small-molecules [67]. Organic semiconducting materials are of interest due to their low processing temperature compatibility, which allows for fabrication on low-cost, flexible substrates [68] such as polyethylene terephthalate (PET) and polyethylene naphthalate (PEN). Reported field effect mobilities for OTFTs are in the range of  $0.1 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  up to  $10 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , whereas *p*-type semiconductors usually show improved performance and reliability in contrast to their *n*-type counterparts [68].

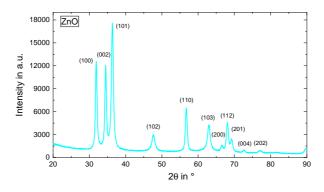

Printed, inorganic TFTs incorporate semiconductors such as metal oxides and silicon. Printed *n*-type metal oxide semiconductors, formed from precursor salts, enable TFTs with high field effect mobilities, exceeding  $100 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  [69]. However, a drawback is the high processing temperature of 200 °C - 500 °C [69]. To reduce processing temperature for precursor-based metal oxide semiconductor fabrication, chemical [70] or photonic curing [71] methods are required, which however also impact field effect mobility. Nanoparticle-based inorganic semiconductors can be sintered at lower temperatures, which allow for fabrication on PET and PEN substrates. For inorganic TFTs, *n*-type semiconductors show increased performance in comparison to *p*-type semiconducting materials [72]. However, printed TFTs generally require operating voltages exceeding 3 V, even when employing high mobility semiconductors.

In inkjet-printing, fabrication of the gate insulator material often yields a bottleneck. Inkjet-printed dielectrics usually require relatively thick layers to prevent leakage currents and shortages between the gate and source-/drain electrodes as well as the gate and semiconductor channel of the TFT. This often leads to small gate capacitance per unit area, which impacts drain current as technology related parameter. To tackle these issues, at the cost of maximum device operating speed, electrolytes can be deployed as insulating material. Electrolyte-gated transistors are capable to reduce operating voltage requirements drastically and enable sub-voltage operation [73–76].

#### 2.2.1.1 Inkjet-Printed Electrolyte-Gated Transistors

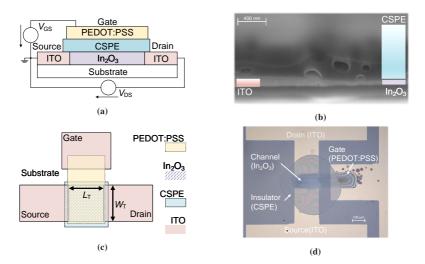

The basis for device and material composition of inkjet-printed electrolyte-gated transistors, also labeled as electrolyte-gated field-effect transistors (EGFETs), were demonstrated by Garlapati et al. using in-plane device structures [73]. Later, Marques et al. presented classical top-gate bottom-contact stack TFT-architecture fabricated EGTs, using lithographically-structured electrodes and interconnects, which show better dynamic device performance including inverter output swing and device switching speed [77, 78].

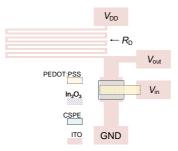

The EGT device material stack consists of an indium tin oxide (ITO) signal routing layer, which forms the drain and source electrodes. Furthermore, indium oxide ( $In_2O_3$ ), as high mobility, inorganic *n*-type semiconductor is deployed. As insulating layer a composite solid polymer electrolyte (CSPE), which is capable to follow the rough semiconductor surface, is used [73]. The increased surface roughness of the indium oxide thin-film is assumed to be influenced by the slow evaporation of water, which is the main solvent of the inkjet-printable precursor fluid [73]. The top-gate consists of the conductive polymer poly(3,4ethylenedioxythiophene):poly(styrenesulfonate) (PEDOT:PSS).

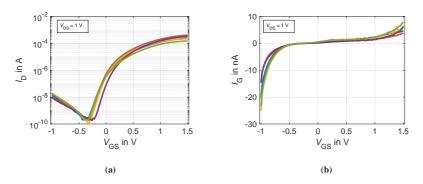

Electrolyte-gated transistors operate in accumulation of charges at the semiconductor/electrolyte interface (SEI) within the semiconductor surface, by applying a positive voltage at the gate-electrode terminal [75]. Due to the occurring migration of ions in the electrolyte, electrical double layers (EDLs) at the top-gate/electrolyte interface (TGEI) and the SEI are formed. Whereas anions, within the electrolyte, migrate towards the positively charged TGEI interface and cations towards the SEI interface, which leads to the aforementioned accumulation of charges in the semiconductor, which enables a current to flow between the drain and source electrodes [79]. The nanometer-sized distances of the resulting capacitor plates, at both EDLs, result in a large gate capacitance per unit area [74]. The combination of a large gate-capacitance per unit area due to the CSPE, and a high field-effect mobility of the semiconductor allow EGTs to generate drain currents ( $I_D$ ) ranging from hundreds of  $\mu$ A to mA at low operating voltages ( $\leq 1.5$  V) [80].

Inkjet-printed EGTs typically operate at several tens of Hz up to kHz [77, 78]. Advances in materials can further increase device switching speed. Currently, the limiting factor in device switching speed is the cutoff-frequency, which arises from the electrolyte-gating approach and is heavily influenced by the top-gate and bulk-electrolyte resistance [81]. Lately, research advancing and highlighting the capabilities of EGTs, due to device modeling with respect to direct-current (DC) characteristics and transistor variability [82,83], EGT capacitance modeling [84], noise characteristics [85] and circuit designs [80,86], have been shown.

### 2.2.2 Printed Circuits

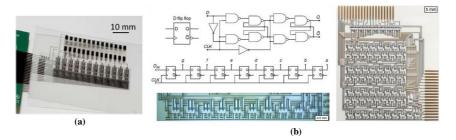

Advanced printed digital circuits, such as D-flip flops [87] and address decoders [88] (see Figure 2.4a), using OTFTs are reported. Furthermore, analog building blocks for small signal amplification such as operational [89–91] and transimpedance amplifiers [91], were successfully presented.

Of special interest are tags for radio frequency identification (RFID), which are one of the many application scenarios where printed TFTs can be employed. Passive RFID designs operating at the 13.56 MHz frequency band, incorporating printed inorganic TFTs, are successfully demonstrated [92]. These presented results are fabricated with devices, employing dielectrics as insulating material. Operating voltages range from 5 V - 20 V.

Low-voltage circuits based on printed electrolyte-gated transistors are increasingly gaining interest. Reported results are mainly on digital circuits such as logic gates, ring oscillators and storage elements [76, 86]. Furthermore, complex systems

incorporating digital logic circuitry with monolithically integrated electrochromic displays [93] are reported and shown in Figure 2.4b. Operating voltages are  $\leq 2 V$ , at operation frequencies reaching from several up to hundreds of Hz.

Figure 2.4: Advanced circuits based on printed TFTs. (a) Printed OTFT-based address decoder and ferroelectric memory on flexible substrate, connected with rigid printed circuit board (PCB) [88]. Reproduced under CC BY-NC-ND 3.0 license, https://creativecommons.org/licenses/by-nc-nd/3.0/. (b) Electrochemically-gated transistors deployed in addressing circuitry for an integrated electrochromic display [93]. Reproduced under CC BY 4.0 license, https://creativecommons.org/licenses/by/4.0/.

# 3 New Concepts in Printed Electronics

In this chapter, new concepts for PE are introduced, with a focus on current trends and requirements for future PE-based applications. Therefore, PE-based solutions for sustainable energy are suggested with a focus on small alternating voltage rectification. In order to enable novel paradigms in computing, current trends are introduced, which are empowered using memristors. Furthermore, printed physically unclonable functions as hardware-based security primitive are discussed.

## 3.1 Sustainable Energy with Printed Rectifiers

With an ever increasing amount of electronic devices joining the IoT worldwide, an increase in environmentally harmful electronic waste is expected [94, 95]. Therefore, ecologically sustainable solutions for electronic devices are required. Autonomous operating systems could be partially equipped with micro energy harvesting devices, which are capable to generate energy from natural resources. This increases lifetime of batteries, which are required for complex, wireless information exchanging, systems [96].

Printed-electronics based solutions for energy harvesting could be equipped on various non-conformal surfaces over large areas and be attached on systems in motion. For self-powered micro systems, vibration energy harvesters, operating at frequencies from tens of Hz to kHz, have proven an interesting option [97–100]. However, micro energy harvesters, such as vibration energy harvesters, output low

alternating voltages, which makes efficient rectification for micro power systems a challenging task [101]. This is often tackled using sophisticated, active Sibased ICs [102, 103]. Comparable rectifier solutions using printed electronics for alternating sub-voltage rectification have not been presented, yet.

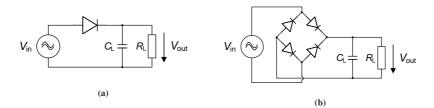

Figure 3.1: Basic passive rectifier circuit schematics, including a capacitor for rectified voltage smoothing and a resistive load. (a) Schematic for a half-wave rectifier, incorporating a single diode. (b) Schematic for a full-wave rectifier, incorporating four diodes.

Rectifiers are fundamental electronic building blocks for signal and power conversion [80]. For PE, mainly rectifier circuits with a focus on frequencies in the MHz range for radio frequency identification are researched to enable smart tags on flexible substrates [80]. Reported, printed solutions often require high voltages in the range of 20 V peak-to-peak ( $V_{pp}$ ). This is attributed to large forward voltage drops in printed diodes and high threshold voltages in printed transistors. As mainly high frequency responses are reported, the voltage-loss due to damping of the input radio frequency signal, over the printed devices at higher frequencies further influences the required input voltages. Nonetheless, the reported high-speed devices aren't capable to rectify low alternating voltages generated from e.g. micro energy harvesting devices. Also, most reported printed rectifiers are realized as passive half-wave rectifier circuits (see Figure 3.1a), with only a few passive full-wave rectifiers (see Figure 3.1b) reported [104], despite their better power conversion efficiency (PCE) [80].

With passive RFID tags as target application, many printed rectifiers are based on multistage voltage multiplier topologies, such as modified Dickson charge pumps, which are commonly used for RFID input signal rectification, in order to provide high DC output voltage levels for the following circuit stages [105–107]. Rectifiers, fabricated using printing technology, are shown in Table 3.1, which includes the rectifier type, rectifying element, printing technology, input voltage, targeted frequency and year of publication. Direct comparison of different works and performance metrics, which are heavily dependent on the targeted application and utilized load, is not straightforward. Furthermore, as mainly RFID capable rectifier solutions for PE are targeted, also printed voltage multiplier topologies are included in the table.

| Туре                                     | Rectifying element    | Printing<br>technology | Input voltage $(V_{\rm pp})$ | Target frequency<br>(Hz) | Year | Ref.  |

|------------------------------------------|-----------------------|------------------------|------------------------------|--------------------------|------|-------|

| Half-wave rectifier & voltage multiplier | Diode (Schottky)      | Gravure & Inkjet       | 20                           | 13.56 M                  | 2010 | [92]  |

| Voltage multiplier                       | TFT (diode-connected) | Screen                 | 40                           | 13.56 M                  | 2012 | [108] |

| Half- & full-wave rectifier              | Diode (Schottky)      | Gravure                | 20                           | 100 k - 13.56 M          | 2013 | [104] |

| Voltage multiplier                       | Diode (Schottky)      | Gravure                | 20                           | 13.56 M                  | 2014 | [109] |

| Voltage multiplier                       | TFT (Vth-cancelling)  | Screen                 | 60                           | 13.56 M                  | 2015 | [110] |

| Half-wave rectifier & voltage multiplier | Diode (Schottky)      | Inkjet                 | 20                           | 13.56 M                  | 2020 | [111] |

Table 3.1: Reported printed rectifiers and voltage multipliers.

## 3.2 New Paradigms in Computing using Memristors

With the trend of Si-based integrated device scaling reaching its physical limits and amounts of data are increasing, new paradigms for future computing systems emerged. This includes Beyond-von-Neumann data processing and neural networks. Furthermore, NAND-flash as non-volatile storage element is reaching its physical limitations, with respect to integration density, speed and reliability [112].

To tackle the aforementioned problems, memristors have shown a promising option [113]. Memristors offer the capability for emulating synaptic plasticity, programmable (multi)-bit information storage and large-scale integration using crossbar architectures. Current trends in research and fabrication is mostly based

on high-density integration of nanometer devices using advanced manufacturing. Furthermore, usability of PE-based neuromorphic computing primitives are shown feasible [114] as well as the need for PE-based, lightweight non-volatile memory. Printed memristors can be utilized to enable Beyond-von-Neumann-, neuromorphic- as well as memory applications in printed electronics.

The theoretical framework and foundations of the memristor, a combination of the words memory and resistor, was formulated by Chua in the form of a dynamical system [115–117]. In 2008 researchers report on a physically realized memristor, which exhibits resistive switching behavior in titanium dioxide crosspoint structures, linking Chua's theory to a practical implementation [118]. Resistive switching behavior in metal oxides has been reported before and was proposed to be utilized in memory applications [119–121]. Non-volatile memory, based on resistive switching devices, is also referred to as (non-volatile) resistance random access memory [122]. However, the systematical link to the memristor, as introduced by Chua was missing. In a retrospective the previously reported devices can also be labeled as memristors or memristive devices [123]. The discovery of the memristor by Strukov et al. boosted research in resistive switching devices heavily, due to the massive potential highlighted by Chua's initial theoretical works.

Resistive switching mechanisms can occur due to various effects, such as amorphouscrystalline phase change, magnetoresistive effects and nanoionic redox phenomena [124]. In the following, focus is on resistive switching caused by nanoionic redox phenomena.

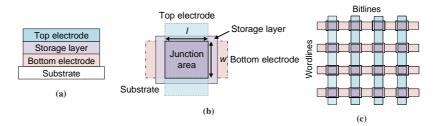

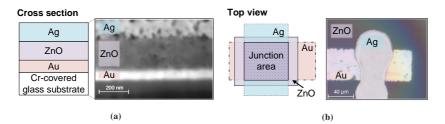

A memristor is usually built in a stacked material architecture. In its most basic form, only two metal electrodes and a single storage material layer are required for device formation, as shown in Figure 3.2a. The storage layer is based on insulating or semiconducting material, whereas the electrodes are mostly metals [122]. The device is capable to obtain at least two distinctive resistive states, a low-resistance state (LRS) and high-resistance state (HRS), based on applied voltage. The resistive state remains programmed within the device until the next programming phase, which enables non-volatile information storage. The device junction area is based on the top and bottom electrode crossing junction, in which

Figure 3.2: Conceptual memristor schematics. (a) Cross section of a memristor material stack. (b) Top-view of a basic resistive switching device stack including the junction area in which resistive switching occurs, based on the overlap in bottom electrode (w) and top electrode (l). (c) Memristors arranged in a crossbar architecture.

the storage layer is sandwiched in, as shown in Figure 3.2b. In this area, interfacial effects can occur, which enables area-based switching, or stochastic filament formation within a fraction of the area is possible. Furthermore, it describes the minimal fabrication possibilities of certain manufacturing technologies. Areabased switching usually occurs close to one electrode and is referred to as interfacetype switching, whereas current is proportional to the effective active area. If the switching mechanism is based on formation and dissolution of a conducting filament it's referred to as filamentary switching [124]. High density integration of devices can be achieved using crossbar architectures, as shown in Figure 3.2c. Filamentary-type switching in memristors is possible mainly due to migration of ions, which lead to formation of a conducting filament/path within the storage layer, which connects both electrodes (low-resistance state) and can be dissolved again (high-resistance state). These effects are based on a different primary mechanism thus devices are named electrochemical metallization memory (ECM) and valence change memory (VCM) [125]. For ECM, cations drift from an active metal electrode such as silver and copper, which lead to metal nano-filament formation. In VCM devices, often metal oxides with high ion mobility, oxygen ion or metal cation migration within the metal oxide leads to redox reaction along with a change in electric conductivity, due to valance change in the cation sublattice [126].

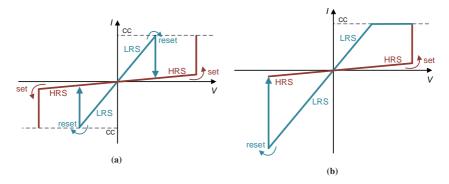

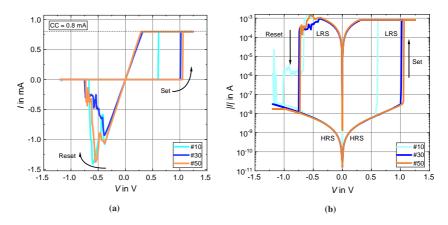

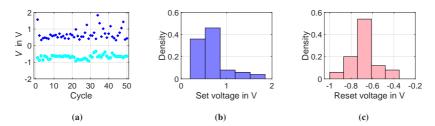

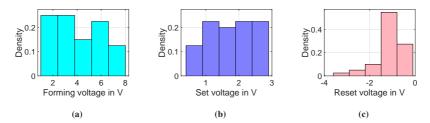

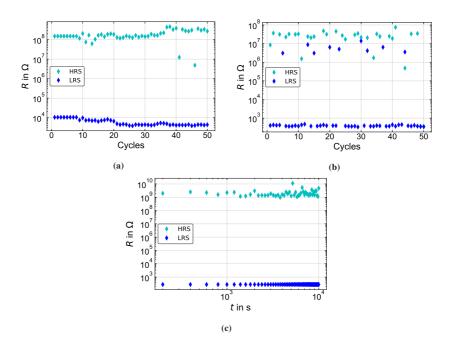

Many ECM-based memristors require an initial forming voltage, which leads to the formation of the conductive filament. This forming voltage usually exceeds the set voltage, which is applied to switch the devices from HRS to LRS. Furthermore, a reset voltage is used to switch the devices from LRS to HRS again. The most common switching-type behavior can be distinguished between unipolarand bipolar switching and is observable in current-voltage (I - V) device characteristics. Unipolar switching behavior is given, when the applied voltage polarity is identical for set and reset processes, as visualized in Figure 3.3a. In bipolar switching, opposite voltage polarities are required to enable device switching. Figure. 3.3b, shows a bipolar switching process, where a positive voltage is required for the set and a negative voltage is required for the reset process. Usually, a compliance current (CC) is required to limit the current over the device and prevent breakdown or device degradation when the memristor switches from HRS to LRS.

Figure 3.3: Typical switching behavior of memristors, including compliance current for current limiting, when the device switches from HRS to LRS. (a) Unipolar device switching. Set and reset voltages have the same polarities. (b) Bipolar device switching. Set and reset voltages require opposite polarities.

# 3.3 Hardware-Based Security with Physically Unclonable Functions

Hardware-based security builds the basis for security in electronic devices in general. With software-sided security being extremely effective at low computational overhead, hardware-based security receives less attention. This is due to the possibly increased overhead in hard- and software, cost and at high performance electronic systems, such as CPUs, also reduced speed. The popular, non-invasive, cache-based side-channel attacks Meltdown and Spectre [127, 128] impressively demonstrated how sensitive information, at the very fundamental levels of data processing within modern, assumable secure, CPU architectures can be exploited due to leaky hardware. This highlights the need for hardware-based security.

With PE-enabled devices joining the IoT, hardware-based security primitives for these devices have to be investigated at the very beginning of their product lifecycle.

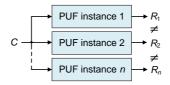

Physically unclonable functions are hardware-security primitives, which enable secure identification, authentication and can be utilized for cryptographic purposes [129–136]. A PUF generates a random sequence of bits, namely response (R), in dependency of an input challenge (C) and based on the intrinsic variations within a stimulated system. The one-way functionality of a PUF can be described as R = f(C) [129, 137, 138] and is unique for each physical instance of the PUF [130], as visualized in Figure 3.4.

Figure 3.4: Schematic for response R generation over different PUF instances of the same type, stimulated with an identical challenge C. Due to intrinsic, unpredictable PUF instance behavior, the output response differs for each PUF instance.

The challenge-response generation and correlation is also referred to as challengeresponse pair (CRP). The volatility of the PUF CRP generation procedure offers an advantage against invasive attacks in comparison to non-volatile electrically erasable read-only-memories, which are commonly used for secret key storage [130].

PUFs can be further classified as either weak or strong PUFs. In weak PUFs the CRPs scale polynomially, based on the exploited variation footprint, whereas strong PUFs show an exponential increase in CRPs dependent on exploited variation footprint. Therefore, for weak PUFs, only a small amount of CRPs can be generated from a PUF instance. Weak PUFs are primarily employed for identification and cryptographic purposes. To obfuscate the resulting challenge-response generation procedure, hashing can be utilized. This operating mode is called controlled PUF [139]. Strong PUFs allow to utilize different challenges, within one PUF instance, in order to generate different and independent responses, thus resulting in a large CRP space [137, 140]. For strong PUFs, the CRP generation does not utilize hashing, as each challenge is capable to deliver a different response. Strong PUFs are mainly used for authentication purposes.

As possible variation sources for PUFs, various surfaces and materials can be stimulated via optical methods, which act as the challenge C and being digitized, to generate a response R. PUFs of this type can be categorized as optical PUFs. Pappu et al. proposed one of the first PUF-related concepts, exploiting randomized speckle patterns for key generation, using optical methods [141]. Optical PUFs are capable to derive large responses at small areas, however often sophisticated external instrumentation is required to achieve high quality, reproducible responses [142]. This can result in high equipment requirements and precise mechanical alignment of the stimulation source and the exploited imperfect surface. Recently, novel material optical PUFs exploiting variation in random, inkjet-printed patterns incorporating fluorescent quantum dots, are presented by Liu et al. [143]. Many novel materials provide surfaces and properties in general that can be exploited using optical methods [144–149].

Another broadly researched field for PUFs are Si-based PUFs [131]. These type of PUFs exploit the explicit intrinsic variations in ICs to generate a response. Physical sources for manufacturing induced variation in Si-based PUFs can be numerous. For metal-oxide-semiconductor field-effect transistors (MOSFETs), the mainly utilized transistor technology within ICs, this includes threshold voltage ( $V_{th}$ ) variation due to random dopant placement [150–152], oxide-thickness [153], channel-area dependent errors [150, 154] and line edge roughness [155–157]. These variations impact device switching speed and drain current. Further down-scaling in MOSFET gate length, besides increasing gate-leakage currents and short-channel effects, impact transistor variability even further. Passive components in ICs, such as poly-resistors and metal-oxide-semiconductor capacitors as well as interconnects, are subject to variation [158–162]. The idea in exploiting IC intrinsic variation for key generation was proposed by Lofstrom et al. [163].

The first systematic concept for PUFs in silicon was presented by Gassend et al. [131, 135, 164], exploiting variations in digital circuitry. Silicon-based PUFs can be categorized in analog-PUFs, which often employ amplifying and device biasing techniques to exploit  $V_{\rm th}$  -impact on transistor drain current in the form of analog circuit design [165–169]. Delay-based PUFs [170, 171] exploit variation in device switching speeds and are more oriented in digital circuits, such as ring oscillator [172–174] and arbiter structures [175, 176]. Furthermore, bistable PUFs often employ cross-coupled inverter configurations, which are commonly used for memory implementations, such as static random-access memory (SRAM) [177–179], in order to generate a response.

Recently, novel material PUFs, utilizing variations with respect to novel materials and devices in the form of Si-based PUFs are emerging. Therefore, variations in electrical characteristics of these devices and circuits are exploited. This includes carbon nanotube (CNT) transistor variation [180, 181], switching type and connection yield in CNTs [182], CNT resistive variation [183], memristors [184–187] and OTFTs [188–191].

For holistic PUF implementation, two main building blocks are required to enable reliable CRP generation. One building block is the so-called PUF core. It

contains a PUF's internal intrinsic variation source. The second PUF building block consists of a control logic for PUF core addressing and readout, which enables CRP generation. However, the control logic is usually also effected by variation, which introduces systematic errors within the PUF. This dilutes PUF core intrinsic variation and negatively impacts PUF metrics. Furthermore, fabricated PUF implementations require error correction strategies for PUF metric optimization [192].

## 3.3.1 Printed Physically Unclonable Functions

Printed electronics often suffers from increased device variation, in comparison to Si-based electronics. The reason is the nature of the manufacturing process, which is based on material processing from a liquid phase. Therefore, registration accuracy of PE-based manufacturing is in general poorer than lithographic processes. Exemplary, variation in active devices, such as printed thin-film transistors, is related to rheology of the printed fluid, quality of interfaces between printed layers such as increased surface roughness, scaling errors in the channel width-to-length ratio and physical layout of a design, to name but a few [89, 90, 193–196]. These factors increase the fabrication-induced as well as intrinsic variation, of printed in comparison to Si-based devices.

Furthermore, PE offers a broad bandwidth of usable substrates, fluids and printing techniques and provides an interesting basis for hardware-based security. However, as variation impacts device and circuit yield, feasible designs for PUF implementations, which extract variation on the electrical signal level (such as Si-based PUF implementations), need to be considered. Thus PUFs utilizing printing technology remain scarce. Especially with a focus on PUF metric evaluation. Mostly single-bit functionalities of these type of PUFs are experimentally verified. Physically unclonable functions, fabricated using printing technology, the PUF type, response generation, corresponding response bit width, experimentally reported PUF metrics and year of publication.

| PUF               | Printing<br>technology | PUF<br>type | -          | - | PUF metrics<br>(experimental) | Year | Ref.  |

|-------------------|------------------------|-------------|------------|---|-------------------------------|------|-------|

| SRAM-PUF          | Screen                 | Weak        | Electrical | 4 | /                             | 2012 | [108] |

| Memory-PUF        | Inkjet                 | Weak        | Electrical | 1 | /                             | 2018 | [197] |

| Resistive CNT-PUF | Inkjet                 | Weak        | Electrical | / | /                             | 2019 | [198] |

| Quantum Dot-PUF   | Inkjet                 | Strong      | Optical    | / | /                             | 2019 | [143] |

**Table 3.2:** Comparison of printed PUFs including reported performance parameters. The absence of a parameter is denoted by (/).

### 3.3.2 Evaluation of Physically Unclonable Functions

To evaluate and compare PUF implementations, performance metrics were proposed by Hori et al. and Maiti et al. [175, 199]. In the following discussion and regarding the results obtained for this thesis, the focus is on PUF metrics introduced by Maiti et al. [199]. This includes the uniqueness, reliability, bit aliasing and uniformity metrics. The hamming distance (HD) is shortly discussed as it provides a fundamental element in PUF metric calculation. Also the bit error metric is shown.

### Hamming distance

The Hamming distance is used to evaluate the amount of different bits between two bit strings of equal length L. Therefore, each l-th bit position between both bit strings is compared by an exclusive or operation and summed up, according to Equation 3.1.

$$HD(x,y) = \sum_{l=0}^{L-1} (x_l \oplus y_l)$$

(3.1)

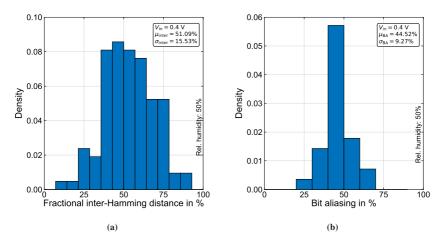

### Uniqueness

To measure the correlation of responses stimulated with the same challenge from different PUF instances, the uniqueness metric is used. The uniqueness is a measure of the PUFs inter-Hamming distance. A uniqueness value of 50% is

optimal, as all PUF responses should differ due to the random intrinsic variations. The uniqueness for N PUFs, incorporating two different PUF instances i and j, each with L-bit responses  $R_i$  and  $R_j$ , is defined as [138, 200]:

$$\mu_{\text{inter}} = \frac{2}{N(N-1)} \sum_{i=1}^{N-1} \sum_{j=i+1}^{N} \frac{\text{HD}(R_i, R_j)}{L} \cdot 100\%$$

(3.2)

#### Reliability

The reliability metric is a measure of the intra-Hamming distance of a PUF and describes the stability of PUF responses under varying operating conditions, such as temperature, noise, humidity and supply voltage, when applying the same challenge. The ideal value is 100 %. The reliability  $\text{REL}_n$  for PUF instance *n* is calculated by using the *L*-bit reference response  $R_{\text{ref},n}$  measured at nominal conditions and the *L*-bit test response  $R'_{n,t}$  for *T* different operating conditions [138, 200]:

$$\operatorname{REL}_{n} = 100\% - \frac{1}{T} \sum_{t=1}^{T} \frac{\operatorname{HD}(R_{\operatorname{ref},n}, R'_{n,t})}{L} \cdot 100\%$$

(3.3)

### Bit aliasing

To evaluate the logic 0's and 1's distribution across different PUF entities of the same type, the bit aliasing metric is used. In an ideal case, both binary values occur with the same probability of 50%. If the *l*-th bit of the tested PUF responses has the same bit value across all PUF entities, the inter-Hamming distance of this bit will be zero. As a result various PUFs may produce the same responses, which degrades the uniqueness and leads to false positives in device authentication. The bit aliasing for N PUF entities at the *l*-th bit position is calculated as [138, 200]:

$$BA_{l} = \frac{1}{N} \sum_{n=1}^{N} R_{n,l} \cdot 100\%$$

(3.4)

#### Uniformity

To evaluate the occurrence of logic 0's and 1's in the PUF responses, the uniformity metric is used. Preferably, both binary values should occur equally often (50%) in a PUF response. For PUF instance n, having an L-bit long response  $R_{n,l}$  at bit position l, the uniformity is defined as [138]:

Uni<sub>n</sub> =

$$\frac{1}{L} \sum_{l=0}^{L-1} R_{n,l} \cdot 100\%.$$

(3.5)

### Bit errors

When generating a PUF response multiple times, bit errors due to flipped bits may occur over time. Reasons are in changing operating conditions over time. Due to possible bit errors, the regenerated CRPs might differ. This degrades both, the uniqueness and the reliability scores. In an ideal case, no bits should flip over time, therefore the optimal value is 0%. Bit errors (BE<sub>n</sub>) are calculated for PUF instance *n* by using the *L*-bit reference response  $R_{ref,n}$  at nominal conditions and the *L*-bit response  $R'_{n,w}$  regenerated *W*-times [138, 200]:

$$BE_n = \frac{1}{W} \sum_{w=1}^{W} \frac{HD(R_{ref,n}, R'_{n,w})}{L} \cdot 100\%$$

(3.6)

# 4 Inkjet-Printed Devices

In this chapter the fabrication routine for inkjet-printed EGTs on laser-ablated ITO substrates, which are used for all obtained results incorporating EGTs during this work, is provided. Furthermore, an inkjet-printed memristor, which provides an important building block for future PE-based circuit and system development, is presented including its fabrication routine and performance evaluation.

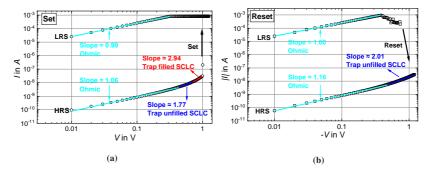

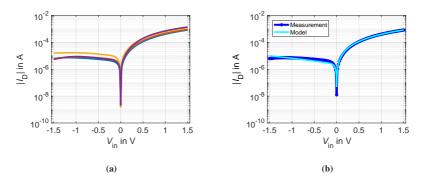

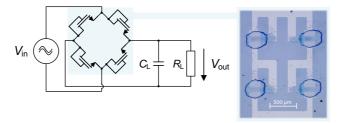

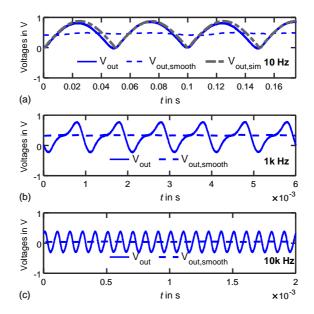

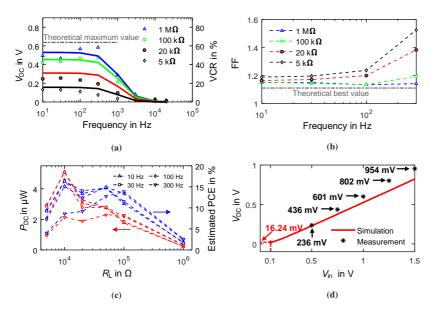

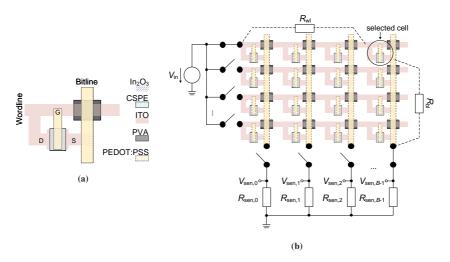

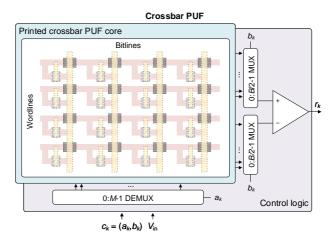

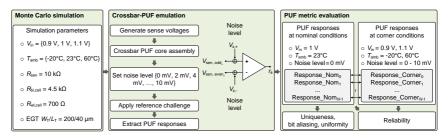

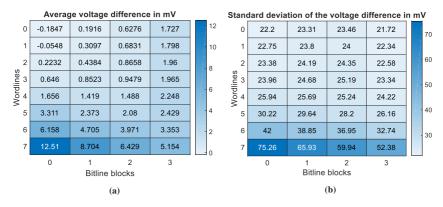

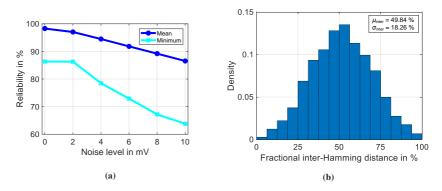

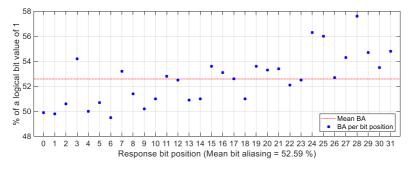

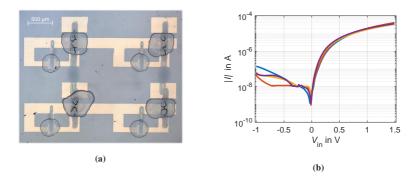

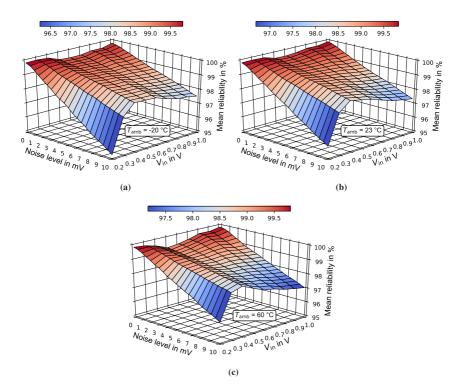

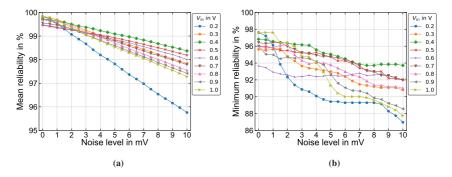

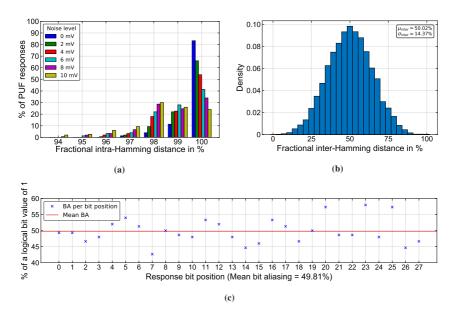

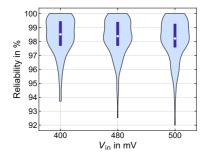

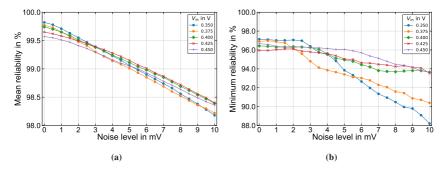

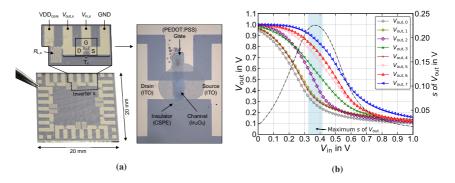

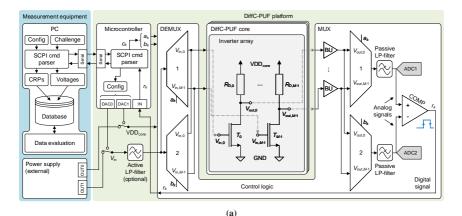

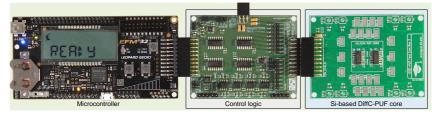

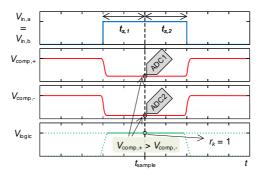

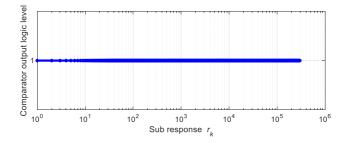

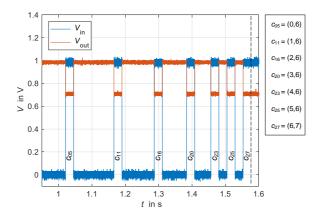

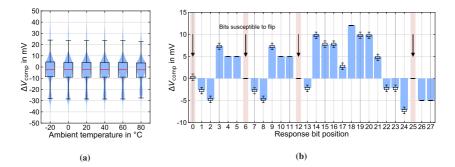

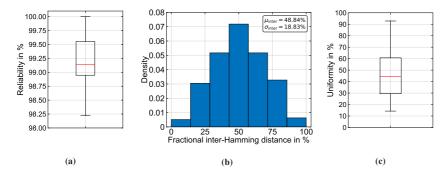

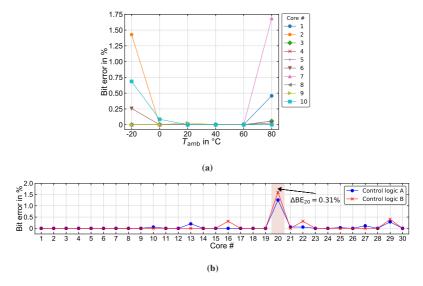

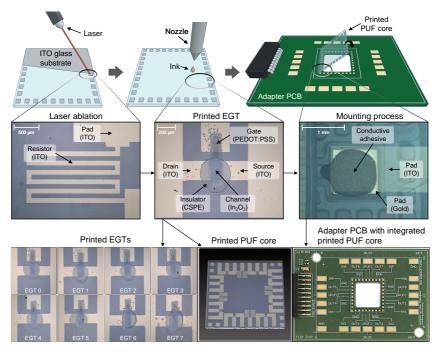

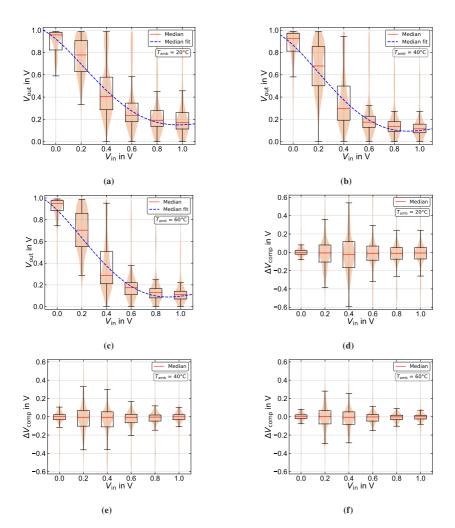

# 4.1 Inkjet-Printed Electrolyte-Gated Transistors