## 1.3 SIRIUS, Der Prozessorkern des ASIC-Design-Centers Offenburg

Prof. Dr.-Ing. Dirk Jansen Dipl.-Ing. (FH) Daniel Bau Dipl.-Ing. (FH) Marc Durrenberger Dipl.-Ing. (FH) Florian Zowislok Dipl.-Ing. (FH) Andreas Kreker

ASIC-Bausteine enthalten heute für die Umsetzung von programmierbaren Funktionen sogenannte Prozessorkerne, die in einer Entwurfssprache wie VHDL oder Verilog beschrieben und mit Synthesetools auf eine gewünschte Zieltechnologie abgebildet werden können. An der Hochschule Offenburg wurde in den letzten Jahren der Prozessorkern SIRIUS entworfen [1] und inzwischen so weit ausgereift, dass er in unterschiedlichen Projekten erfolgreich implementiert werden kann. In der Zieltechnologie AMI 0,35 ist er z.B. in dem ePillen-Chip enthalten. Als Softcore kann er auch mit gleicher Funktionalität in einem FPGA implementiert werden.

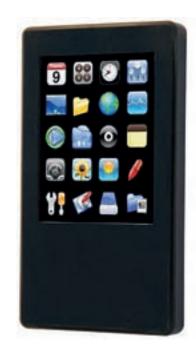

Zur Demonstration der Leistungsfähigkeit des Kerns wurde in 2008 ein Personal-Digital-Assistent PDA entwickelt, der den SIRIUS-Kern in einem Cyclon III-FPGA der Firma ALTERA enthält. Dies ist unseres Wissens der erste PDA mit einem FPGA, siehe Abbildung 1.3-1.

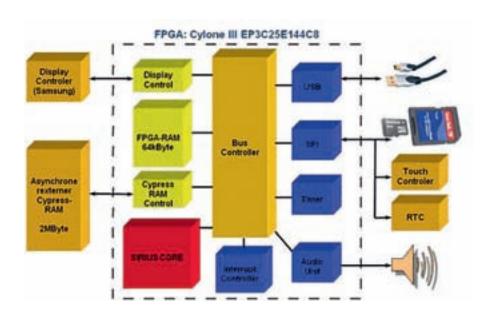

Die Platine (Abbildung 1.3-2), entwickelt in der Diplomarbeit von Andreas Kreker, ist auf etwa 51 x 50 mm geschrumpft und enthält zusätzlich noch einen Controller für den Touchscreen, einen Ausgangsverstärker für einen Lautsprecher zur Wiedergabe von Musik sowie eine Speichererweiterung von 2 MB für den sonst komplett im FPGA implementierten SIRIUS-Kern.

Der Prozessor arbeitet mit einer Frequenz von 48 Mhz. Ein Fullspeed USB-Bus-Anschluss ermöglicht das Downloaden von Programmen. Abbildung 1.3-3 zeigt ein Blockschaltbild des PDAs. Über die Entwicklung wurde auf dem Workshop der MPC-Gruppe ausführlich berichtet. Das kleine ebenfalls in Offenburg entwickelte Betriebssystem SIRIUS-OS [2] ermöglicht den Aufruf von Applikationen durch Berühren der entsprechenden Ikonen. Apple IPod lässt grüßen! [4]

Abb. 1.3-1: PDA mit grafischer Touchscreen-Oberfläche, entwickelt an der Hochschule Offenburg mit dem eigenen Prozessorkern SIRIUS, 32 bit, 48 MHz, ca. 40 MIPS Leistung auf einem programmierbaren Cyclon III FPGA

**Abb. 1.3-2:** Platine für den Betrieb des PDAs, Abmessungen 50 x 51 mm, USB, Tonausgabe, 2 Mbyte Hauptspeicher, OLED Display 320 x 240, 64k Farben, Touchscreen, MicroSD-Karte, 48 MHz, 5 h Betriebszeit mit Akku und Display On

Derzeit werden weitere Applikationen für den IAF-PDA geschrieben (MP3, JPEG), ein Bild-Viewer, ein Wave-Player sowie eine Uhrzeitanzeige bestehen bereits. Durch die C-Programmierbarkeit des SIRIUS-Prozessors und die verfügbaren Softwaretools steht die gesamte Welt der C-Bibliotheken prinzipiell zur Verfügung.

Die nächste Generation dieses für die Studenten attraktiven Projekts wird eine Erweiterung des SIRIUS-Kerns um einen Cache-Speicher und der Anschluss eines mobilen DDR-RAMs sein, was den PDA endgültig in eine kommerziell nutzbare Dimension weiterentwickeln wird. Das PDA-Projekt demonstriert sichtbar, welche Möglichkeiten in der Elektronik heute auch für ein kleines Team bestehen.

Ein PDA ist nicht nur ein interessantes Forschungsobjekt, sondern vor allem für die Lehre ein faszinierendes technisches Spielzeug, mit dem Studenten für modernste Elektronikentwicklung begeistert werden können.

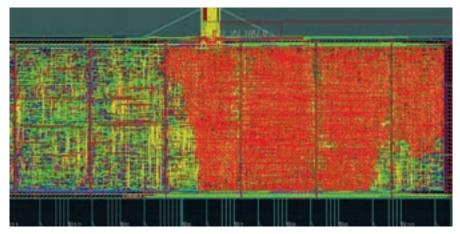

In Abbildung 1.3-4 ist der SIRIUS-Prozessorkern in einem ASIC-Layout (< 1 mm2) zu sehen.

## Referenzen

- [1] Jansen D., Fawaz N., Durrenberger M., Bau D.: "A Small High Performance Microprocessor Core SIRIUS For Embedded Low Power Designs, Demonstrated in a Medical Mass Application Of an Electronic Pill (ePille®)", Embedded System Design Topic, Techniques and Trends, ISBN 978-0-387-72257-3, p. 363–372, California, USA, June 2007

- [2] Kreker A.: Entwicklung eines PDA-Demonstrators mit OLED Display, Touchscreen und grafischer Bedienoberfläche mit dem im FPGA implementierten Softcore SIRIUS, August 2008

- [3] Zowislok F., Jansen D.: SIRIUS-OS, Betriebssystem für das SIRIUS-Emulationsboard, Technischer Bericht 04/2008, IAF, HS-OG, Oktober 2008

- [4] Jansen D., Kreker A.: "Grafische Oberfläche für SIRIUS-Prozessorkern auf FPGA", Hochschule Ulm, MPC-Workshop in Künzelsau, Februar 2009

**Abb. 1.3-3:** Blockschaltbild des im FPGA integrierten Elektronikteils. Bis auf wenige Hilfsschaltkreise ist alles im FPGA enthalten, der damit aber erst zu 45% gefüllt ist

Abb. 1.3-4: SIRIUS-Prozessorkern in einem SOC-Design