# **Entwicklung eines synchronen Transceivers mit DQPSK-**Modulation und Soft Shift Keying für eine induktive Übertragung mit Erprobung in einem FPGA

M. Mogel, D. Jansen, N. Fawaz, ASIC Design Center Offenburg Hochschule Offenburg, Badstraße 24, D-77652 Offenburg Tel.: 0781/205-274

Ziel dieses Projektes war die Entwicklung einer induktiven. synchronen Datenübertragungsstrecke basierend auf einem bereits vorhandenen. asynchronen Modell. Einige Komponenten wurden ausgetauscht, verbessert oder konnten in angepasster Form übernommen werden.

# 1. Einleitung

#### Projekt "ePille<sup>®</sup>"1 1.1.

Das Projekt "ePille®,1" der Hochschule Offenburg befasst sich mit der Entwicklung eines oral einführbaren Mikrochips, der es ermöglichen soll, Medikamente gezielt an den menschlichen Körper abzugeben. Die Steuerdaten dieser "ePille®" sollen synchron und induktiv übertragen werden. Das ASIC Design Center besitzt auf diesem Gebiet der Übertragungstechnik einige Erfahrungen und Hintergrundwissen.

#### 1.2. **Transceiverkonzept**

Das Kernstück des synchronen DQPSK Transceivers bildet die neue SYN SIO (synchron serial in/out). Ihre Aufgabe ist es, die Daten so zu verpacken, dass sie möglichst schmalbandig und fehlerfrei übertragen werden können. Vorgesehen ist eine Datenrate von 9,6 kBaud. Anschließend werden die Daten mit einer Trägerfrequenz von 115,2 kHz DQPSK moduliert und an die Empfängerspule gesendet. Die Empfangsseite und die Sendeseite unterscheiden sich im Wesentlichen nur durch die jeweiligen Register bzw. Ansteuerung. Per Soft Shift Keying soll ein möglichst schmalbandiger Phasenwechsel erzielt werden.

# 2. Die SYN SIO

#### 2.1. **Datenrahmen**

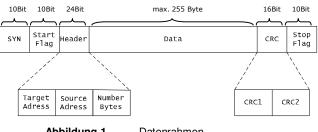

Als Datenrahmen wurde folgende Struktur festgelegt:

Abbildung 1 Datenrahmen

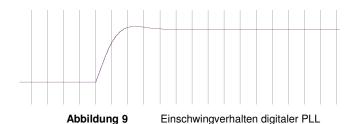

Am Anfang jedes Datenrahmens wird eine Bitfolge von '0' und '1' im Wechsel gesendet. Diese Flankenwechsel werden benötigt, um den PLL, der zur Taktrückgewinnung dient, einschwingen zu lassen. Anhand dieser Flankenwechsel wird der PLL so geregelt, dass der Empfänger immer in der Mitte eines Bits abtastet und somit eine Phasenverschiebung von 180° im Vergleich zum Sendetakt aufweist. Das anschließende START FLAG dient der Erkennung eines Datenrahmens auf der Empfängerseite. Sie sucht die Datenleitung nach genau dieser speziellen Bitkombination ab. Wird sie als START FLAG detektiert, wird das nächste Byte, die Zieladresse, per Protokoll ausgewertet. Stimmt die Zieladresse mit der des Empfängers überein, werden die Daten byteweise RAM abgelegt. Wenn nicht, werden alle einkommenden Bytes ignoriert und die Leitung nach dem nächsten, gültigen START FLAG abgesucht. Der Header beinhaltet des Weiteren die Quelladresse und die Anzahl der gesendeten Bytes. Die Größe der Nutzdaten ist auf 255 Bytes begrenzt. Eine 16 Bit Prüfsumme im Anhang der Nutzdaten gibt Aufschluss

MPC-Workshop, Juli 2006

<sup>1 &</sup>quot;ePille®" ist ein eingetragenes Warenzeichen des IAF

über den Erfolg der Übertragung. Ein abschließendes STOP FLAG beendet den Datenrahmen, wird ebenfalls detektiert und zeigt dem Empfänger an, dass die Übertragung beendet ist.

# 2.2. Funktionsweise SYN SIO

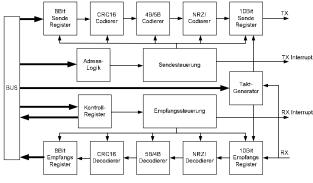

Der Aufbau der SYN SIO ist weitgehend symmetrisch gehalten. Sowohl die Sende- als auch die Empfangsseite verfügt über je 2 Register. Das jeweilige 8 Bit Register bildet die Schnittstelle zum Datenbus.

Abbildung 2 Blockschaltbild SYN SIO

Damit eine synchrone Datenübertragung fehlerfrei und zuverlässig arbeiten kann, ist es notwendig, den Sendetakt auf der Empfängerseite zu rekonstruieren. Dies geschieht hier mit Hilfe einer 4B/5B- und NRZI Codierung. Die 4B/5B Codierung wandelt jedes Nibbel in eine 5 Bit Kombination um. Die so entstehende Redundanz erzeugt einen minimalen Fehlerschutz (Haming Distanz=1), vor allem aber werden Bit-Kombinationen erzeugt, die maximal drei '0' Bits in Folge enthalten. Die anschließende NRZI Codierung arbeitet nach folgender Vorschrift:

- Pegelwechsel bei '1'

- kein Pegelwechsel bei '0'

Diese Funktion kann mit Hilfe eines XOR Gatters realisiert werden. Der somit entstandene Datenstrom beinhaltet maximal vier '0' Bits bevor die nächste Flanke kommt und zur Regelung des Empfangs-PLL genutzt werden kann. Die beiden 10 Bit Register bilden die Schnittstelle zum Modulator bzw. Demodulator und somit 7Ur Sendebzw. einen Empfangseinheit. Um kontinuierlichen Datenstrom zu erzeugen, wird das 8 Bit Register vor Senden des letzten Datenbits nachgeladen. Dies geschieht über den TX Interrupt. Über diesen Interrupt wir dem Prozessor mitgeteilt, dass das nächste Byte in das 8 Bit Register geladen werden kann. Auch hier wieder die Analogie zur Empfangsseite. Über einen RX Interrupt wird dem Prozessor signalisiert, dass das nächste Byte im 8 Bit Register zur Abholung bereit liegt. Gesteuert werden die Register über eine separate Sende- und Empfangssteuerung.

Zur Erzeugung der Baudrate wird ein PLL als Taktgenerator eingesetzt. Der kritische Empfangstakt wird mit Hilfe des empfangenen Datenstroms ständig nachgeregelt. Somit wird sichergestellt, dass auch bei unterschiedlichem Systemtakt eine fehlerfreie Datenübertragung gewährleistet ist. Der PLL besitzt einen Fangbereich von über 2,5% des Systemtaktes. Der unkritische Sendetakt wird als MSB vom NCO abgegriffen und kann beliebig über den BUS, am Anfang jeder Übertragung, programmiert werden.

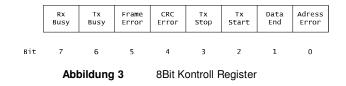

Ein 8 Bit Kontrollregister besitzt unter anderem die Aufgabe, evtl. auftretende Übertragungsfehler zu erkennen und anzuzeigen. Erkannt werden können CRC Prüfsummenfehler und Frame Errors. Frame Errors sind Fehler die auftauchen können, wenn am 4B/5B Codierer oder Decodierer ein ungültiges Eingangs-Nibbel anliegt. Auch ein fehlendes STOP FLAG führt zu einem Frame Error. Damit ein CRC Fehler angezeigt werden kann, muss der Inhalt des CRC-Registers ungleich Null sein. Eine fehlerfreie Übertragung liefert ansonsten eine Null als Ergebnis. Des Weiteren wird über das Kontrollregister das Startbzw. Stopbit zum Starten bzw. Enden einer Übertragung gesetzt. Eine Rx Busy bzw. Tx Busy Bit zeigt jeweils an, ob der Transceiver beschäftigt ist.

# 3. Der Modulator

### 3.1. Funktionsweise Modulator

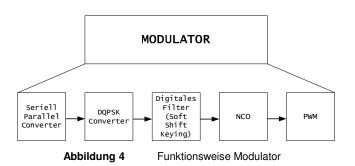

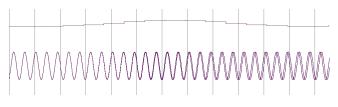

Der 1 Bit Datenstrom wird im ersten Schritt zur weiteren Verarbeitung zu je 2 Bits zusammengefasst. Um die Phasenlage des Senders bzw. Empfängers

nicht berücksichtigen zu müssen, wird lediglich die Phasenänderung, die DQPSK Daten, übertragen. Ein digitales Filter sorgt für eine langsame Phasenänderung. Dieses Signal wird einem NCO zugeführt, welcher in Abhängigkeit von seinem Korrekturwert eine Freguenz zwischen 107-123kHz erzeugt. Eine PWM Einheit generiert das Ansteuersignal für die Sendespule.

#### 3.2. **DQPSK Converter**

Um die beiden zusammengefassten Bits übertragen zu können, sind insgesamt 4 Zustände notwendig. Dabei wurde folgende Zuordnung getroffen:

(1) "00"

$$\rightarrow$$

+45° (3) "01"  $\rightarrow$  +135°

(2) "10"

$$\rightarrow$$

-45° (4) "11"  $\rightarrow$  -135°

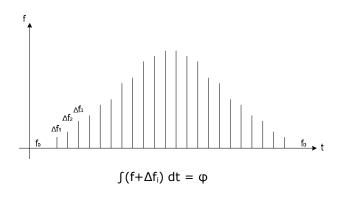

#### 3.3. Soft Shift Keying

Ein digitaler Gauß-Filter wird eingesetzt, um einen langsamen, schmalbandigen Phasenübergang zu erreichen.

Abbildung 5 Gauß-Filter

Das Integral des Filters entspricht einer Frequenzänderung und bewirkt somit einer Phasenverschiebung.

Abbildung 6 Soft Shift Keying

Abb. 6 zeigt im unteren Teil die Trägerfreguenz und das darübergelegte modulierte Signal. Anfangs sind beide noch phasengleich. Die Frequenz des modulierten Signals steigt bzw. sinkt mit dem Gauß-Filter und besitzt nach der Filterung eine Phasenverschiebung von exakt +45°.

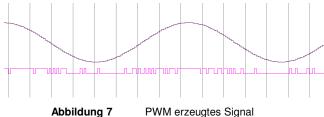

#### 3.4. **PWM**

Zur Ansteuerung der Spule ist es notwendig, eine Folge von '1' und '0' zu erhalten, die es der Spule ermöglicht, ein Sinus-Signal mit der gewünschten Frequenz zu erzeugen. Abb. 7 zeigt die Funktionsweise der PWM-Einheit:

Am Einfachsten ist es, die Extremwerte zu betrachten. Ein Maximum des Sinus bedeutet eine lange '1' Folge, entsprechend eine lange '0' Folge ein Minimum. Die Nullstellen des Sinus entsprechen einer Folge von '1' und '0', deren Mittelwert wiederum Null ergibt.

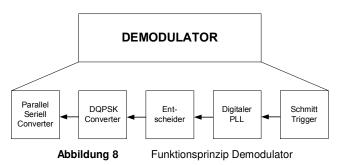

### 4. Der Demodulator

#### 4.1. **Funktionsweise Demodulator**

Nach einer A/D Wandlung mit Hilfe des Schmitt Triggers wird über einen digitalen PLL das Signal demoduliert. Ein Entscheider ordnet der Phasenänderung die jeweiligen Bitkombinationen zu, um nach anschließender DQPSK Convertierung wieder einen 1 Bit Datenstrom zu erhalten.

# 4.2. Digitaler PLL

Die Aufgabe des digitalen PLL ist es, das Empfangssignal, bestehend aus einer Folge von '0' und '1', so zu rekonstruieren, dass der Entscheider die richtigen Phasenänderungen erkennen kann. Das Referenz Signal des PLL ist die Trägerfrequenz von 115,2 kHz. Das empfangene, modulierte Signal weist je nach Bitfolge eine positive bzw. negative Phasenverschiebung zum Trägersignal auf. Das Ausgangssignal des Schleifenfilters wird abgegriffen und liefert das gewünschte, demodulierte Signal. Damit der Regelkreis auch stabil arbeitet, wird bei jeder Korrektur ein Offset (Gleichanteil) hinzuaddiert. Dieser Gleichanteil wirkt sich jedoch nur auf den NCO aus und bewirkt ein schnelles Nachregeln.

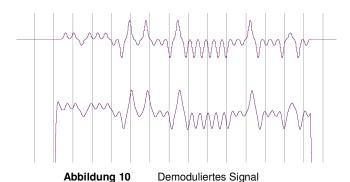

Die Qualität des demodulierten Signals ist in Abb. 10 gut zu erkennen. Das obere entspricht dem gesendeten, das untere dem empfangenen Signal.

### 4.3. Entscheider

Die Aufgabe des Entscheiders ist es, aus dem Signal die entsprechenden Phasenverschiebungen zu erkennen, und somit den Bitkombinationen zuzuordnen.

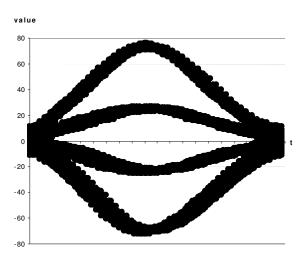

Um die notwendigen Abtastpunkte zu erhalten wird das Signal gleichgerichtet und jeder Bitabschnitt mit 13 Samples abgetastet. Ein FIR Filter dient als Differenzierer und erzeugt bei jedem Maximum (Steigung=0) einen positiven Flankewechsel. Somit kann der Entscheider bei jedem Abtastpunkt den Wert prüfen und, entsprechend einer Look-Up Tabelle, zuordnen. Abb. 11 zeigt das Augendiagramm des demodulierten Signals:

Abbildung 11 Augendiagramm

# 5. Ergebnis

Die Aufgabe, ein stabiles und fehlersicheres System zu entwickeln, wurde hiermit erreicht.

Die Codierung erkennt alle 1 und 2 Bit Fehler, alle ungeraden Bitfehler und alle Fehlerbursts der Länge ≤16 Bit.

Die Fangbereiche der eingesetzten PLL's lassen sich mit folgenden Werten angeben

- SYN SIO PLL ± 2,5 % des Systemtaktes

- Demodulator PLL ± 10 % der Mod.-Frequenz

### 6. Literaturverzeichnis

- [1] Drigalsky, Ingo, "Serielle Schnittstellentechnik" 1991

- [2] Fawaz, Nidal, "Development of CP-DQPSK Modulator and Demodulator using VHDL for inductive data transmission" Master Thesis 2002

- [3] Pehl, Erich, "Digitale und analoge Nachrichtenübertragung" 2001

- [4] Reichardt, J./Schwarz B., "VHDL Synthese" 2003

- [5] Vogel, Daniel, "Entwicklung eines integrierten Buscontroller ASIC's auf der Basis des Mikroprozes-sorkernels FHOP und Demonstration des Bussystems am Beispiel einer Modelleisenbahn" Diplomarbeit 1996